System Overview

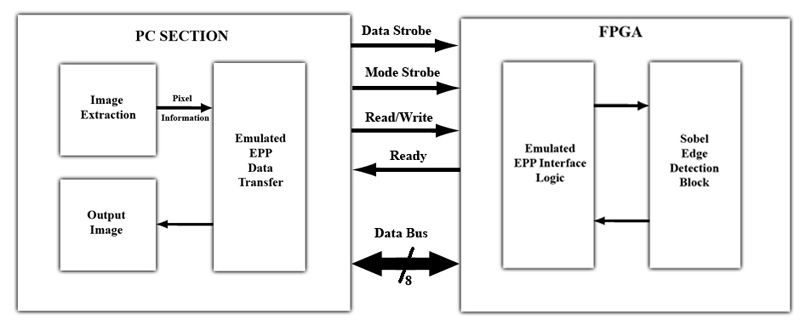

The project essentially consists of manipulating images in order to perform the Sobel Edge detection algorithm. The image of selected formats like .JPEG, .PNG and .BMP are converted to the raw image data using a C program. The image was represented as pixels of 8bits (values ranging from 0 to 255). Once the computer performs the image extraction, the information thus obtained is to be sent to the FPGA in order to perform the mathematical computations. The communication between the computer and the FPGA is done via the parallel port which is operating in bidirectional mode. Appropriate handshake signals are used to eliminate errors in data transfer. As the parallel port operates on TTL logic levels while the FPGA follows the LVCMOS (3.3V), level translation has to be performed. 74LS641 which is an octal bidirectional buffer with open collector I/O was used for the level translation. The Sobel operator is applied on the block of pixels received in the memory. The processed data is transferred to the computer using the parallel port. The data thus received is further manipulated to reconstruct and display the edge detected image. Tags: FPGA , Sobel , Parallel Port , |