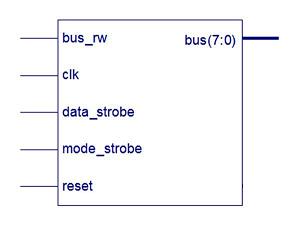

Edge Detection Hardware ArchitectureThe Block gives the overall I/O ports on the edge detection system using fpga.

The bus_rw controls the direction of data transfer while data_strobe and mode_strobe signals control the entire data transfer operation. The clk signal is the internal clock of the FPGA. The bus(7:0) is an 8 bit bidirectional data bus. Internally the system consists of Ram Modules wired to 32 FPGA modules. There are 3 sets of 34byte RAM array which can be serially loaded and parallely shifted. The 3 sets of RAM Array are wired to 32 Sobel Instances Tags: Sobel , FPGA , Edge Detection , Architecture , |